Electronics R&D

Examples of R&D electronics boards & ASIC designs/chips developed by the DPNC electronics/microelectronics group

12-hex SiPM and cones, analog preamplifier & slow control boards for CTA SST-1M telescopes (Astroparticles / Ground)

Front-End Electronics using IGLOO FPGA, 2 CITIROC ASICs and ADCs, HV, Peltier and heater control with 64-ch SiPM array for POLAR-2 experiment / Space grade (Astroparticles / Space)

Arria 10 FPGA Front-End Board with 8 CITIROC ASICs, ADCs, LVDS and Gigabit transceivers for 256-channels (left) and associated test setup emulating Back-End Electronics with adapters and GPIO (right) used for S-FGD sub-detector of ND280 experiment, Japan (Neutrinos)

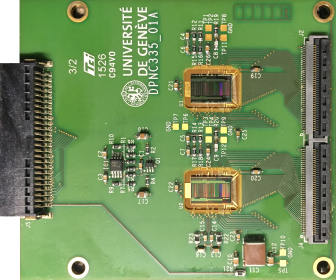

AMS ATLASpix1 monolithic CMOS sensors for the ATLAS Inner Tracker of the LHC, developed in collaboration with several institutes (High Energy Physics)

96-ch SiPM USB3 and Gigabit Link Front-End board with Arria 5 FPGA and 3 CITIROC ASICs for Baby-Mind experiment (Neutrinos)

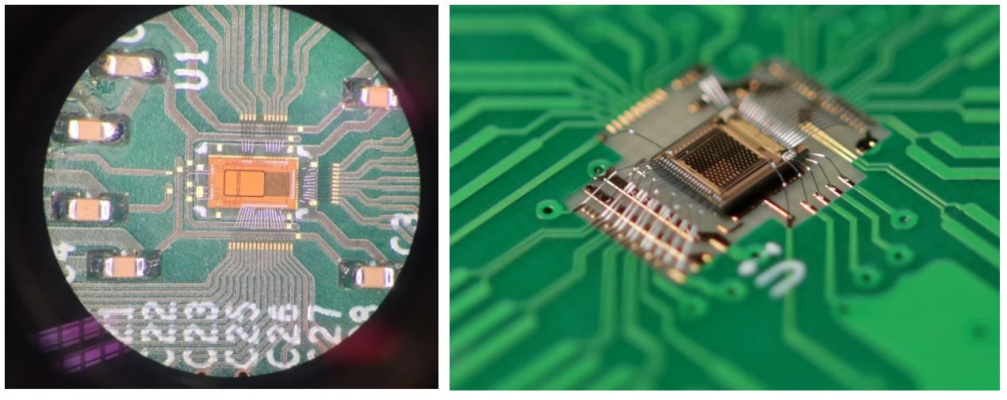

Small prototypes of monolithic pixel sensor using SiGE BiCMOS, designed by DPNC (TT-PET / High Energy Physics)

32-ch 5GSPS DRS4 - USB3 VME format Acquisition Board (Neutrinos)

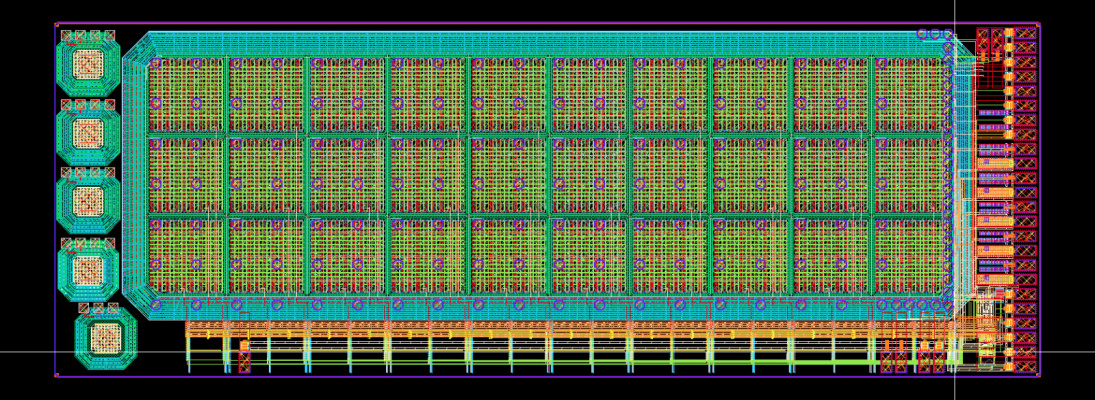

Layout of a fully-featured ASIC with a 3 by 10 pixels matrix for a sub-100 ns Time-of-Flight PET scanner designed by DPNC (TT-PET / High Energy Physics)

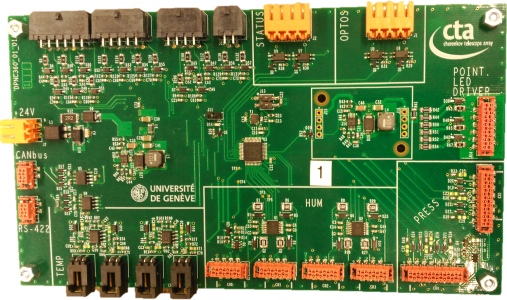

Environmental monitoring board for 12 temperature, 4 humidity and 2 pressure sensors with CAN bus and RS-485 interfaces for SST-1M camera (Astroparticles / Ground)

Unige GPIO board : General Purpose Inputs/Outputs USB3/Ethernet board with Cyclone 5 FPGA used for multiple projects & prototypes readout system

4x2 SiPM HF amplifier + shapping and sum for Time Of Flight sub-detector of ND280 upgrade, Japan (Neutrinos)

Fiber Tracker Readout boards assembly (logic board with nanoXplore FPGA on left, power board on right) for 2x9 Front-End boards for HERD experiment / Space grade (Astroparticles / Space)

Strip-Y Front-End (left) with 1 x 128-ch VATA ASIC, ADC and silicon detector, Zoom on VA140 bonding (centre) and Strip-X Front-End (right) with 32 x 64-ch VA140 ASICs , ADCs and silicon detector for PAN demonstrator (Astroparticles / Space)

8 x SCT modules Tracker Readout Board (left) and Trigger Logic Board (right) using Unige GPIO board for FASER experiment installed at CERN (LHC parallel tunnel)

2 VATA ASICs Front-end board prototype for 128 SiPMs (Astroparticles / Space)

Front End Rigid-Flex with 6 VATA ASICs and 3x128-ch SiPM array for HERD space experiment (Astroparticles / Space)

Slow Control Board with 12-ch HV/LV/temperature control from CAN bus microcontroller for SiPM amplifier (left), backplane for 10 SCB boards (centre) and patch panel board (right) for Time Of Flight sub-detector of ND280 update, Japan (Neutrinos)

Time Of Flight System made of SiPM Rigid-Flex PCB (right), Front-End Electronics with 1 CITIROC and 1 TRIROC ASIC, ADCs and clock synchronization (top left) and GPIO readout system (bottom left) for PAN demonstrator (Astroparticles / Space)

Front End Electronics prototype (left) with 28 IDeF-x and 2 OWB-1 ADCs CEA ASICs, and INFN Silicon Drift Detector, zoom on OWB-1 bonding (right) for eXTP space experiment / Space grade (Astroparticles / Space)

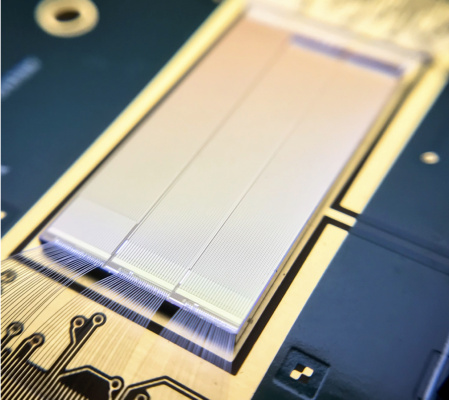

Tracker Front End hybrid for DAMPE space experiment (Astroparticles / Space)

6 FASER-PS prototype ASICs designed by DPNC before assembly (left) onto Module Flex (right) for FASER Pre-shower upgrade of FASER experiment installed at CERN (LHC parallel tunnel)